# MB89352 SCSI Protocol Controller (SPC) with On-Chip Drivers/Receivers

Edition 1.0 September 1989

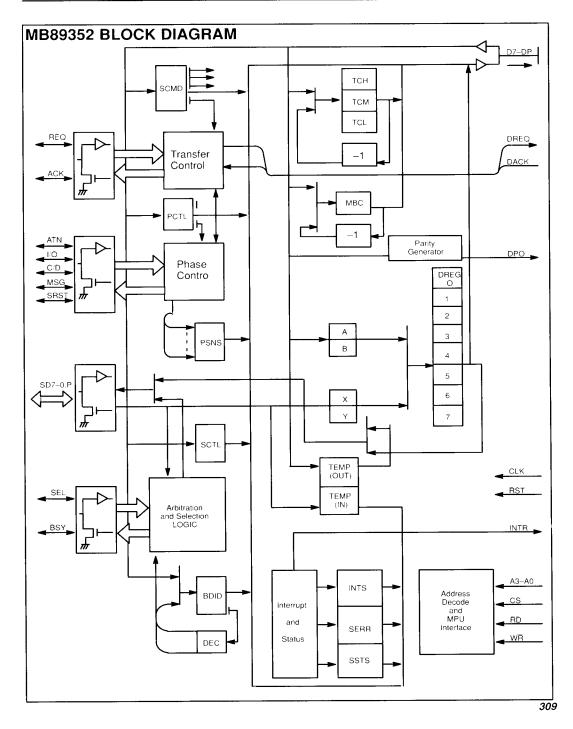

#### GENERAL DESCRIPTION

The MB89352 CMOS LSI SPC (SCSI Protocol Controller) is a circuit designed for easy control of the small computer system interface (SCSI).

The MB89352 can be used as a peripheral LSI circuit for an 8- or 16-bit MPU to realize high-level SCSI control. The SPC can control all the SCSI interface signals and handle almost all the interface control procedures. The on-chip driver/receivers allow for direct connection to the SCSI BUS.

This LSI circuit has an 8-byte FIFO data buffer register and a transfer byte counter that is 24 bits long. Furthermore, the MB89352 can serve as either an INITIATOR or a TARGET device for the SCSI, and can therefore be used for either an I/O controller or a host adapter.

#### **SCSI Compatibility**

- Full support for SCSI control (ANSI X3.1311986 Specification) except for synchronized transfer mode

- Serves as either INITIATOR or TARGET

#### Data Transfer Rate/Byte Counter

- 8-byte FIFO data timing control

- 24-bit transfer byte counter

#### Drive Options (on-chip driver/receiver)

Single-ended

#### Selectable Transfer Modes

- DMA Transfer

- Program Transfer

- Manual Transfer

#### **Clock Requirements**

• 8 MHz clock

#### Technology/Power Requirements

- Silicon-gate CMOS

- Single +5 V power supply

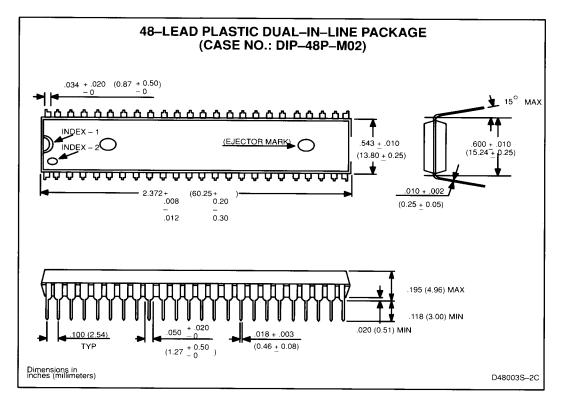

#### Available Packaging

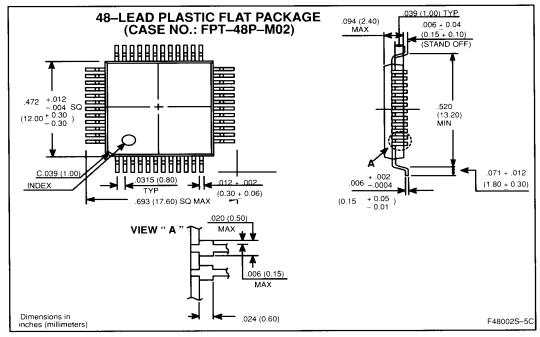

48-pin DIP or FLAT plastic packages

ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Dating                      | Designator       | Valu                 | 11   |      |

|-----------------------------|------------------|----------------------|------|------|

| Rating                      | Designator       | Min.                 | Max. | Unit |

| Supply Voltage              | V <sub>CC</sub>  | V <sub>SS</sub> -0.3 | 7.0  | V    |

| Input Voltage               | V <sub>1</sub>   | V <sub>SS</sub> -0.3 | 7.3  | V    |

| Output Voltage <sup>2</sup> | Vo               | V <sub>SS</sub> -0.3 | 7.3  | V    |

| Storage<br>Temperature      | T <sub>STG</sub> | -55                  | 150  | °C   |

Notes: 1 Permanent device damage may occur if the above absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2 Should not exceed V<sub>CC</sub> + 0.5V.

## RECOMMENDED OPERATING CONDITIONS

|                               | <b>.</b>        |      |      |      |      |

|-------------------------------|-----------------|------|------|------|------|

| Parameter                     | Designator      | Min. | Тур. | Max. | Unit |

| Supply Voltage                | V <sub>cc</sub> | 4.75 | 5.0  | 5.25 | V    |

| Operating Ambient Temperature | T <sub>A</sub>  | 0    |      | + 70 | °C   |

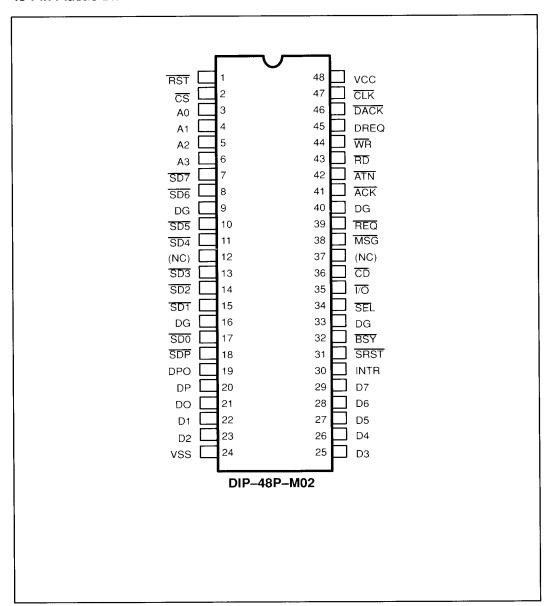

### **PIN ASSIGNMENTS**

#### **48-Pin Plastic DIP**

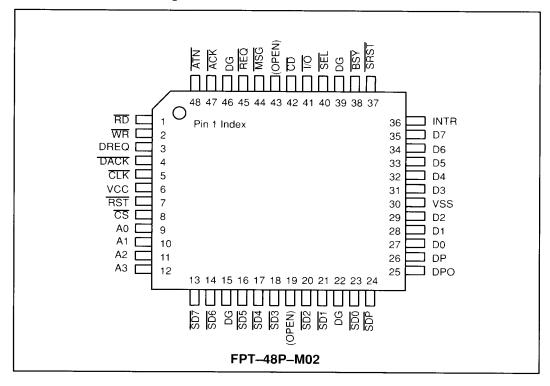

# PIN ASSIGNMENTS (Continued)

## 48-Pin Plastic Flat Package

## **PIN DESCRIPTIONS**

|                                  | Pin N                            | lo.                              |     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------|----------------------------------|----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Designator                       | DIP                              | FPT                              | I/O | runction                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>CC</sub>                  | 48                               | 6                                | _   | +5V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>SS</sub>                  | 24                               | 30                               | -   | Circuit ground.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DG                               | 9<br>16<br>33<br>40              | 15<br>22<br>39<br>46             | _   | Ground (OV) for internal drivers. The SCSI bus drivers can sink up to 48-mA each. Up to 16 drivers can be active at once. We recommend a good solid ground plane.                                                                                                                                                                                                                                                                                    |

| CLK                              | 47                               | 5                                | _   | Clock input for controlling internal operation and data transfer speed of the SPC.                                                                                                                                                                                                                                                                                                                                                                   |

| RST                              | 1                                | 7                                |     | Asynchronous reset signal used to clear all internal circuits of the SPC.                                                                                                                                                                                                                                                                                                                                                                            |

| CS                               | 2                                | 8                                | 1   | Input selection enable signal for accessing an internal register. When active low, the following input/output signals are valid: RD, WR, A3-A0, DP7-DP0 and DP.                                                                                                                                                                                                                                                                                      |

|                                  |                                  |                                  |     | Address input signals for selecting an internal register in SPC. MSB is A3; LSB is A0.                                                                                                                                                                                                                                                                                                                                                               |

| A0<br>A1<br>A2<br>A3             | 3<br>4<br>5<br>6                 | 9<br>10<br>11<br>12              | 1   | When $\overline{\text{CS}}$ is active, read/ write is enabled for an internal register selected by these address inputs via data bus lines D0-D7 and DP.                                                                                                                                                                                                                                                                                             |

| RD                               | 43                               | 1                                |     | This strobe input is used for reading out the contents of the SPC internal register, and is effective only when $\overline{CS}$ input is active. While $\overline{RD}$ is active, the contents of an internal register selected by A0 to A3 inputs are placed on data bus lines D7 to D0, DP. For a data transfer cycle in the program transfer mode, the rising edge of $\overline{RD}$ is used as a timing signal indicating the end of data read. |

| WR                               | 44                               | 2                                | I   | The strobe input is used for writing data into an SPC internal register, and is effective only when CS input is active. On the rising edge of this signal, data placed on data bus lines D0 to D7, DP are loaded into an internal register selected by A0 to A3 inputs. For a data transfer cycle in the program transfer mode, the rising edge of this signal is used as a timing signal indicating data ready status.                              |

| DP<br>D0<br>D1<br>D2<br>D3<br>D4 | 20<br>21<br>22<br>23<br>25<br>26 | 26<br>27<br>28<br>29<br>31<br>32 | I/O | Used to write/read data to/from an internal register in the SPC. The data bus is 3-state and bidirectional. The MSB is D7 and the LSB is D0; DP is an odd parity bit.  When both CS and RD inputs are active, the contents of a selected internal register are output to the data bus. In op-                                                                                                                                                        |

| D5<br>D6<br>D7                   | 27<br>28<br>29                   | 33<br>34<br>35                   |     | erations other than read/write, the data bus is kept at a high-Z level.                                                                                                                                                                                                                                                                                                                                                                              |

Continued on following page

# **PIN DESCRIPTIONS**

| Burtana                                                     | Pin I                                      | No.                                                | Ī.,_ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------|--------------------------------------------|----------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Designator                                                  | DIP                                        | FPT                                                | 1/0  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DPO                                                         | 19                                         | 25                                                 | 0    | Outputs an odd parity of D0–D7. If parity bit is not generated for external memory, DPO can be used as an input parity bit for DP.                                                                                                                                                                                                                                                                                                                                                                     |

| INTR                                                        | 30                                         | 36                                                 | 0    | The INTR output signal is issued by the SPC and requests an interrupt to indicate completion of an internal operation or the occurrence of an error. Except for an interrupt caused by the RSTI input (reset condition in SCSI).                                                                                                                                                                                                                                                                       |

|                                                             |                                            |                                                    |      | When an interrupt request is granted, the INTR signal remains active until the interrupt is cleared.                                                                                                                                                                                                                                                                                                                                                                                                   |

| DREQ                                                        | 45                                         | 3                                                  | 0    | For a data transfer cycle in DMA mode, this signal is used to indicate a request for data transfer between the SPC and the external buffer memory. In an output operation, this signal becomes active to request a data transfer from the external buffer memory when the SPC internal data buffer register has free space available. In an input operation, it becomes active to request data transfer to the external buffer memory when the SPC internal data buffer resgister contains valid data. |

| DACK                                                        | 46                                         | 4                                                  | ı    | An active low response signal to the DREQ which request data transfer in between SPC and the external memory in the DMA mode. This signal in DMA mode functions similarly to the signal combination of CS=low, A3=high, A2=low, A1-high, and A0=low (selection of DREG) in the program transfer mode. Since the DREG is selected by this DACK signal in the DMA mode instead of the address input from A3-A0, data transfer in between DREG of SPC and external memory is possible.                    |

| SD0<br>SD1<br>SD2<br>SD3<br>SD4<br>SD5<br>SD6<br>SD7<br>SDP | 17<br>15<br>14<br>13<br>11<br>10<br>8<br>7 | 23<br>21<br>20<br>18<br>17<br>16<br>14<br>13<br>24 | I/O  | Active low bi-directional SCSI data bus.  MSB: SD7, LSB: SDO Odd parity bit : SDP  Parity check for the SCSI data bus is programmable.                                                                                                                                                                                                                                                                                                                                                                 |

| SEL                                                         | 34                                         | 40                                                 | I/O  | A signal to issue or detect selection or reselection phase. In selection phase, an initiater asserts this signal, and in reselection phase the signal is asserted by the target.                                                                                                                                                                                                                                                                                                                       |

| BSY                                                         | 32                                         | 38                                                 | I/O  | This signal indicates the SCSI bus use condition. This signal goes "L" when SPC is in arbitration phase or working as a target. Also, this signal is used to detect bus free phase with SEL signal.                                                                                                                                                                                                                                                                                                    |

Continued on following page

# **PIN DESCRIPTIONS**

|                   | Pin                    | No.            |     |                                                                                                                                                                                                                                                                                            |                           | Func          | ation                                                                                                   |  |

|-------------------|------------------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------|---------------------------------------------------------------------------------------------------------|--|

| Designator        | DIP                    | FPT            | 1/0 |                                                                                                                                                                                                                                                                                            |                           | runc          |                                                                                                         |  |

| I/O<br>C/D<br>MSG | 3 <b>5</b><br>36<br>38 | 41<br>42<br>44 |     | as follow                                                                                                                                                                                                                                                                                  | 'S:                       |               | e of information transfer phase                                                                         |  |

|                   |                        |                | 1/0 | MSG                                                                                                                                                                                                                                                                                        | C/D                       | 1/0           | Phase Name                                                                                              |  |

|                   |                        |                |     | 0                                                                                                                                                                                                                                                                                          | 0                         | 0             | Data Out Phase                                                                                          |  |

|                   |                        |                |     | 0                                                                                                                                                                                                                                                                                          | 0                         | 1             | Data In Phase                                                                                           |  |

|                   |                        |                |     | 0                                                                                                                                                                                                                                                                                          | 1                         | 0             | Command Phase                                                                                           |  |

|                   |                        |                |     | 0                                                                                                                                                                                                                                                                                          | 1                         | 1             | Status Phase                                                                                            |  |

|                   |                        |                |     | 1                                                                                                                                                                                                                                                                                          | 0                         | 0             | Reserved                                                                                                |  |

|                   |                        |                |     | 1                                                                                                                                                                                                                                                                                          | 0                         | 1             | Reserved                                                                                                |  |

|                   |                        |                |     | 1                                                                                                                                                                                                                                                                                          | 1                         | 0             | Message Out Phase                                                                                       |  |

|                   |                        |                |     | 1                                                                                                                                                                                                                                                                                          | 1                         | 1             | Message In Phase                                                                                        |  |

| REQ               | 39                     | 45             | 1/0 | These signals are output from the target and initiator receives them always.  In the data transfer phase, the REQ signal is used to notify the INITIATOR that the TARGET is ready to receive or send data. The REQ input is used as a timing control signal in the data transfer sequence. |                           |               |                                                                                                         |  |

| ACK               | 41                     | 47             | I/O | sponse t<br>In the sa                                                                                                                                                                                                                                                                      | o a transf<br>ime way a   | er request (f | acknowledge signal is in re-<br>REQ) signal from the TARGET.<br>ACK input is used as a timing<br>uence. |  |

| ATN               | 42                     | 48             | I/O |                                                                                                                                                                                                                                                                                            | to indicati<br>om an init |               | ondition. This signal is only                                                                           |  |

| SRST              | 31                     | 37             | 1/0 |                                                                                                                                                                                                                                                                                            |                           |               | ed by register setting. SCSI is non-maskable.                                                           |  |

| NC                | 12, 37                 |                | _   | Not con                                                                                                                                                                                                                                                                                    | nected                    |               |                                                                                                         |  |

| OPEN              | _                      | 19, 43         |     | Reserve                                                                                                                                                                                                                                                                                    | d. (Do no                 | t make exter  | rnal connections to these pins)                                                                         |  |

Fast Track to SCSI MB89352

#### ADDRESSING OF INTERNAL REGISTERS

SPC has internal registers, consisting of 15 bytes, that are accessible from an external circuit. These internal registers are used for controlling SPC internal operation and indicating SPC processing status/result status. A unique address is assigned to each internal register, and a particular register is identified by address bits A3 to A0. The following table shows internal register addressing:

Table 1. Internal Register Addressing

| Register               | Mnemonic   | Operation | Chip Select<br>(CS) | А3 | Addre<br>A2 | ss Bits  | Α0 |

|------------------------|------------|-----------|---------------------|----|-------------|----------|----|

| negistei               | Willemonic |           | (03)                | AS | A2          | AI       | AU |

| Bus Device ID          | BDID       | R         | 0                   | 0  | 0           | 0        | 0  |

|                        |            | W         |                     |    |             |          |    |

| SPC Control            | SCTL       | R         | 0                   | 0  | 0           | 0        | 1  |

| Si o control           | SOIL       | W         | Ŭ                   | U  | U           | J        |    |

| Command                | SCMD       | R         | 0                   | 0  | 0           | 1        | 0  |

| Command                | SCIVID     | W         | U                   | 0  | U           | •        | U  |

| Open                   |            |           | 0                   | 0  | 0           | 1        | 1  |

|                        |            |           |                     |    |             |          | ·  |

| Interrupt Sense        |            | R         | _                   | _  |             |          | _  |

| Reset Interrupt        | INTS       | W         | 0                   | 0  | 1           | 0        | 0  |

| Phase Sense            | PSNS       | R         | 0                   | 0  | . 1         | 0        | 1  |

| SPC Diagnostic Control | SDGC       | W         |                     | U  | ,           | 0        | '  |

| SPC Status             | SSTS       | R         | 0                   | 0  | 1           | 1        | 0  |

|                        |            | W         |                     |    | <u>'</u>    | <u>'</u> | Ü  |

| SPC Error Status       | SERR       | R         | 0                   | 0  | 1           | 1        | 1  |

| _                      |            | W         |                     |    |             |          |    |

| Phase Control          | DOT        | R         |                     |    |             |          | 0  |

| Phase Control          | PCTL       | w         | 0                   | 1  | 0           | 0        | 0  |

| Modified Byte Counter  | мвс        | R         | 0                   |    |             |          | 4  |

| _                      |            | W         | 0                   | 1  | 0           | 0        | 1  |

Continued on following page

Table 1. Internal Register Addressing

|                          |          |           | Chip Select |            | Addre | ss Bits    | ,  |

|--------------------------|----------|-----------|-------------|------------|-------|------------|----|

| Register                 | Mnemonic | Operation | (CS)        | <b>A</b> 3 | A2    | <b>A</b> 1 | Α0 |

| Data Register            | DREG     | R         | 0           | 1          | 0     | 1          | 0  |

| Data Hegister            | DNLG     | W         | Ŭ           | •          | 0     |            | 5  |

| Towns are Desister       | TEMP     | R         | 0           | 1          | 0     | ,          | 4  |

| Temporary Register       | I CIVIF  | W         | 0           |            | U     | '          | ,  |

| Transfer Counter High    | тсн      | R         | 0           | 1          | 1     | 0          | 0  |

| Transfer Counter riigii  | TOH      | W         | U           | •          | ,     |            | 0  |

| Transfer Counter Middle  | TCM      | R         | 0           | 1          | 1     | 0          | 1  |

| Transfer Gourner Wildale | 70101    | w         | -           | ,          | ,     | 1 0        |    |

| T ( )                    | TO:      | R         |             | 1          |       |            |    |

| Transfer Counter Low     | TCL      | W         | 0           | '          | 1     | 1          | 0  |

#### **BIT ASSIGNMENTS**

The following table shows the bit assignments to each internal register. When accessing an internal register (in read/write), remember the following:

- The internal register block includes the read—only/write—only register and those having different meanings in read and write operations.

- A write command to a read—only register is ignored.

- 3. If the write—only register is read out, the data and parity bit are undefined.

- 4. At bit positions indicating "\_" for a write in either 1 or 0 may be written.

Table 2. Bit Assignments for Internal Registers

| HEX<br>Address | Register<br>and<br>Mnemonic    | R/W<br>Oper-<br>ation | 7<br>(MSb)              | 6                     | 5               | 4                              | 3                        | 2                | 1                       | 0<br>(LSb)              | Parity |

|----------------|--------------------------------|-----------------------|-------------------------|-----------------------|-----------------|--------------------------------|--------------------------|------------------|-------------------------|-------------------------|--------|

| 0              | Bus<br>Device ID               | R                     | #7                      | #6                    | #5              | #4                             | #3                       | #2               | #1                      | #0                      | 0      |

|                | (BDID)                         | W                     |                         |                       |                 |                                |                          | ID4              | ID2                     | ID1                     |        |

| 1              | SPC<br>Control<br>(SCTL)       | R/W                   | Reset<br>& Dis-<br>able | Con-<br>trol<br>Reset | Diag<br>Mode    | ARBIT<br>Enable                | Parity<br>Enable         | Select<br>Enable | Resel-<br>ect<br>Enable | INT<br>Enable           | Р      |

|                | Command                        | R                     | 0                       |                       |                 | RST<br>Out                     | Inter-<br>cept           | Tran:<br>PRG     | sfer Mo                 | difer<br>Term           | Р      |

| 2              | (SCMD)                         | W                     | Com                     | mand Co               |                 | Out                            | Xfer                     | Xfer             | 0                       | Mode                    | P      |

| 3              |                                | R<br>W                |                         |                       |                 |                                |                          |                  |                         |                         |        |

| 4              | Interrupt<br>Sense             | R                     | Selec-<br>ted           | Resel-<br>ected       | Discon-<br>nect | Com-<br>mand<br>Comp-<br>plete | Service<br>Re-<br>quired | Time<br>Out      | SPC<br>Hard<br>Error    | Reset<br>Condi-<br>tion | Р      |

|                | (SERR)                         | W                     |                         |                       | Re              | eset Inter                     | rupt                     |                  |                         |                         | _      |

| _              | Phase<br>Sense<br>(PSNS)       | R                     | REQ                     | ACK                   | ATN             | SEL                            | BSY                      | MSG              | C/D                     | I/O                     | Р      |

| 5              | SPC Diag.<br>Control<br>(SDGC) | W                     | Diag.<br>REQ            | Diag<br>ACK           | Xfer<br>Enable  |                                | Diag.<br>BSY             | Diag.<br>MSG     | Diag.<br>C/D            | Diag.<br>I/O            | _      |

| 6              | SPC<br>Status                  | R                     | Conr                    | ected<br>TARG         | SPC<br>BSY      | XFER<br>In Pro-<br>gress       | SCSI<br>RST              | TC=0             | DREG<br>Full            | Status<br>Empty         | Р      |

|                | (SSTS)                         | W                     |                         |                       |                 |                                |                          |                  |                         |                         |        |

Continued on following page

# **Bit Assignments For Internal Registers**

| HEX<br>Address | Register<br>and<br>Mnemonic | R/W<br>Oper-<br>ation | 7<br>(MSb)               | 6                                 | 5          | 4               | 3              | 2             | 1          | 0<br>(LSb) | Parity |

|----------------|-----------------------------|-----------------------|--------------------------|-----------------------------------|------------|-----------------|----------------|---------------|------------|------------|--------|

| 8              | Phase                       | R                     | Bus<br>Free              |                                   |            |                 |                | Trans         | fer Phase  |            |        |

| 8              | Control<br>(PCTL)           | W                     | Inter-<br>rupt<br>Enable |                                   |            | )               |                | MSG<br>Out    | C/D<br>Out | 1/O<br>Out | Р      |

| 9              | Modified<br>Byte<br>Counter | R                     |                          |                                   | 0          |                 | Bit 3          | MB<br>Bit 2   | C<br>Bit 1 | Bit 0      | Р      |

| 9              | (MBC)                       | W                     |                          |                                   |            |                 |                |               |            |            | Р      |

| A              | Data<br>Register            | R                     |                          |                                   | Internal [ | Data Reg        | jister (8 E    | yte FIFO      | )          |            |        |

| A              | (DREG)                      | W                     | Bit 7                    | Bit 6                             | Bit 5      | Bit 4           | Bit 3          | Bit 2         | Bit 1      | Bit 0      | Р      |

|                |                             | R                     |                          | Temporary Data (Input: From SCSI) |            |                 |                |               |            |            |        |

| В              | Temporary                   |                       | Bit 7 j                  | Bit 6                             | Bit 5      | Bit 4           | Bit 3          | Bit 2         | Bit 1      | Bit 0      | Р      |

|                | Register<br>(TEMP)          | W                     |                          |                                   | Tempora    | ary Data        | (Output:       | To SCSI)      |            |            |        |

|                | ( )                         | •                     | Bit 7                    | Bit 6                             | Bit 5      | Bit 4           | Bit 3          | Bit 2         | Bit 1      | Bit 0      | Р      |

| С              | Transfer<br>Counter         | R                     |                          |                                   | <br>Trans  | fer Cour        | l<br>nter High | (MSB)         | ļ          | l          |        |

|                | High<br>(TCH)               | w                     | Bit 23                   | Bit 22                            | Bit 21     | Bit 20          | Bit 19         | Bit 18        | Bit 17     | Bit 16     | P      |

| D              | Transfer<br>Counter<br>Mid  | R                     |                          |                                   | Transfer   | <b>C</b> ounter | Middle (       | l<br>2nd Byte | 1          | Ī          |        |

|                | (TCM)                       |                       | Bit 15                   | Bit 14                            | Bit 13     | Bit 12          | Bit 11         | Bit 10        | Bit 9      | Bit 8      | Р      |

| E              | Transfer<br>Counter         | R                     |                          | Transfer Counter Low (LSB)        |            |                 |                |               |            |            |        |

|                | LOW<br>(TCL)                | w                     | Bit 7                    | Bit 6                             | Bit 5      | Bit 4           | Bit 3          | Bit 2         | Bit 1      | Bit 0      | Р      |

These bit assignments for the MB89352 internal registers are identical to those in the MB87030, MB87031, and MB89351. Therfore, SPC replacement from one to another is very easy and does not require any new software design.

Fast Track to SCSI MB89352

# DC CHARACTERISTICS (Ta=0-70°C, Vcc=5V ±5%) (Recommended operating conditions unless otherwise specified)

## **SCSI Bus Signal Pins**

| _                      |                 |                                                   |      | Values |      |      |  |

|------------------------|-----------------|---------------------------------------------------|------|--------|------|------|--|

| Parameter              | Designator      | Conditions                                        | Min. | Тур.   | Max. | Unit |  |

| Input High Voltage     | V <sub>IH</sub> |                                                   | 2.0  | _      | 5.25 | ٧    |  |

| Input Low Voltage      | V <sub>IL</sub> |                                                   | 0    | _      | 0.8  | ٧    |  |

| Input High Current     | l <sub>IH</sub> | V <sub>IH</sub> + 5.25V                           | _    | 100    | 400  | μΑ   |  |

| Input Low Current      | liL             | V <sub>IL</sub> + OV                              | _    | -100   | -400 | μΑ   |  |

| Output Low Voltage     | V <sub>OL</sub> | V <sub>CC</sub> = 4.75V<br>I <sub>OL</sub> + 48mA | _    | _      | 0.5  | V    |  |

| Input Hysteresis Width | V <sub>HM</sub> |                                                   | 0.2  | 0.4    | _    | ٧    |  |

## **MPU Bus Signal Pins**

|                       |                  |                                             |                      | Values |                       |          |

|-----------------------|------------------|---------------------------------------------|----------------------|--------|-----------------------|----------|

| Parameter             | Designator       | Conditions                                  | Min.                 | Тур.   | Max.                  | Unit     |

| Input High Voltage    | V <sub>IH</sub>  |                                             | 2.2                  |        | V <sub>CC</sub> + 0.3 | <b>V</b> |

| Input Low Voltage     | V <sub>IL</sub>  |                                             | V <sub>SS</sub> -0.3 | _      | 0.8                   | ٧        |

| Output High Voltage   | V <sub>OH</sub>  | I <sub>OH</sub> + 0.4 mA                    | 4.0                  |        | V <sub>CC</sub>       | ٧        |

| Output Low Voltage    | V <sub>OL</sub>  | I <sub>OL</sub> + 3.2 mA                    | V <sub>SS</sub>      |        | 0.4                   | ٧        |

| Input Leakage Current | I <sub>LIH</sub> | V <sub>IH</sub> + 5.25                      |                      |        | 20                    | μΑ       |

| input Leakage Current | 1 <sub>LIL</sub> | V <sub>IL</sub> + 0.0                       |                      |        | -10                   | μΑ       |

| Input/Output Leakage  | I <sub>LZH</sub> | V <sub>IH</sub> + 5.25                      |                      |        | 40                    | μΑ       |

| Current               | I <sub>LZL</sub> | V <sub>IL</sub> + 0.0                       |                      |        | -40                   | μΑ       |

| Power Supply Current  | Icc              | Input Clock = 8 MHz<br>All Output Pins Open |                      |        | 10                    | mA       |

## (Recommended operating conditions unless otherwise noted)

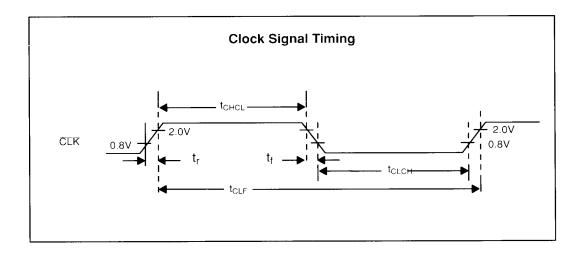

## **Clock Signal**

| CLK Input             | 444               |      |        |      |      |

|-----------------------|-------------------|------|--------|------|------|

| _                     |                   |      | Values |      | Unit |

| Parameter             | Designator        | Min. | Тур.   | Max. |      |

| CLK Cycle Time        | talf              | 125  |        | 200  | ns   |

| CLK High Time         | tснсг             | 44   |        |      | ns   |

| CLK Pulse Width       | t <sub>сьсн</sub> | 44   |        |      | ns   |

| CLK Rising Skew Time  | t,                | -    |        | 10   | ns   |

| CLK Falling Skew Time | t i               |      |        | 10   | ns   |

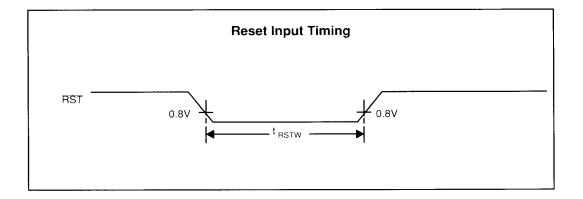

| RST Input       |            |        |      |      |      |

|-----------------|------------|--------|------|------|------|

| _               |            | Values |      |      |      |

| Parameter       | Designator | Min.   | Тур. | Max. | Unit |

| RST Pulse Width | trstw      | 100    |      |      | ns   |

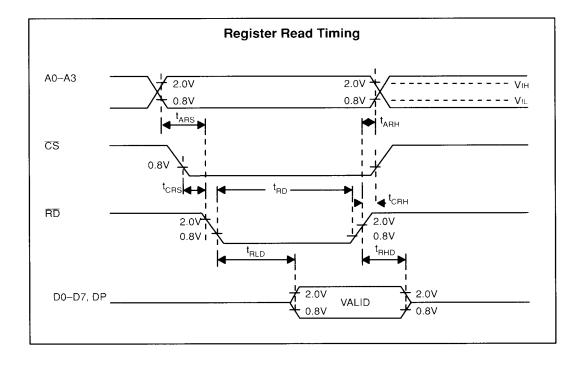

| Register Read                                           |                  |      |      |      |      |

|---------------------------------------------------------|------------------|------|------|------|------|

|                                                         |                  |      |      |      |      |

| Parameter                                               | Designator       | Min. | Тур. | Max. | Unit |

| Address Setup Time                                      | t <sub>ARS</sub> | 40   |      |      | ns   |

| Address Hold Time                                       | t <sub>ARH</sub> | 10   |      |      | ns   |

| CS Setup Time                                           | t <sub>CRS</sub> | 25   |      |      | ns   |

| CS Hold Time                                            | t <sub>CRH</sub> | 10   |      |      | ns   |

| Data Valid Time (from RD Low) (C <sub>L</sub> = 80pF)   | t <sub>RLD</sub> |      |      | 90   | ns   |

| Data Valid Time (from RD Hi gh) (C <sub>L</sub> = 20pF) | t <sub>RHD</sub> | 10   |      | 60   | ns   |

| RD Pulse Width                                          | t <sub>RD</sub>  | 120  |      |      | ns   |

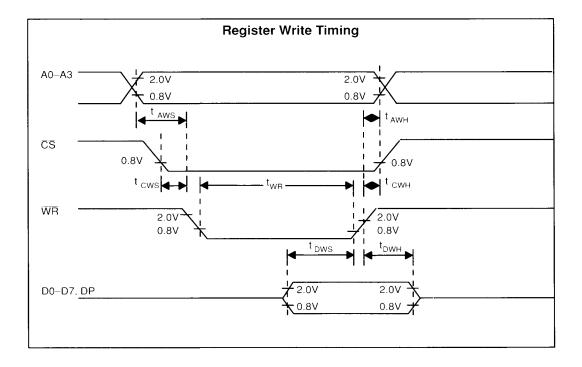

| Register Write      |                  |      |        |      |      |

|---------------------|------------------|------|--------|------|------|

| _                   |                  |      | Values |      |      |

| Parameter           | Designator       | Min. | Тур.   | Max. | Unit |

| Address Setup Time  | taws             | 40   |        |      | ns   |

| Address Hold Line   | t <sub>AWH</sub> | 10   |        |      | ns   |

| CS Setup Time       | t <sub>cws</sub> | 25   |        |      | ns   |

| CS Hold Time        | t <sub>CWH</sub> | 10   |        |      | ns   |

| Data Bus Setup Time | t <sub>DWS</sub> | 30   |        |      | ns   |

| Data Bus Hold Time  | t <sub>DWH</sub> | 20   |        |      | ns   |

| WR Pulse Width      | t <sub>WR</sub>  | 100  |        |      | ns   |

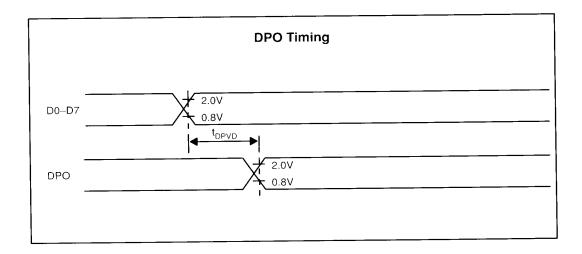

| DPO (Data Parity Output)              |                   |                 |                 |        |      |      |

|---------------------------------------|-------------------|-----------------|-----------------|--------|------|------|

|                                       |                   |                 |                 | Values |      | 11   |

| Parameter                             | Designator        | Test Conditions | s Min. Typ. Max |        | Max. | Unit |

| Data Bus (D0 – D7) Valid to DPO Valid | t <sub>DPVD</sub> | CL = 30pF       |                 |        | 60   | ns   |

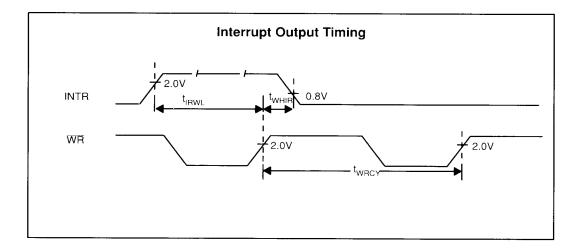

| INTR (Interrupt Request) Out          | put                        |           |                   | -      |                         | •  |

|---------------------------------------|----------------------------|-----------|-------------------|--------|-------------------------|----|

| Parameter                             |                            |           |                   | Values |                         |    |

| Parameter                             | Designator Test Conditions | Min.      | Тур.              | Max.   | Unit                    |    |

| WR High to INTR Low (Interrupt reset) | t <sub>whiR</sub>          | CL = 10pf | t <sub>CLF</sub>  |        | 2t <sub>CLF</sub> + 100 | ns |

| INTR High to WR High                  | t <sub>IRWL</sub>          |           | 0                 |        |                         | ns |

| INTR Reset Cycle Time <sup>1</sup>    | t <sub>WRCY</sub>          |           | 4t <sub>CLF</sub> |        |                         | ns |

**Note:** <sup>1</sup>Applicable only when interrupt reset is executed.

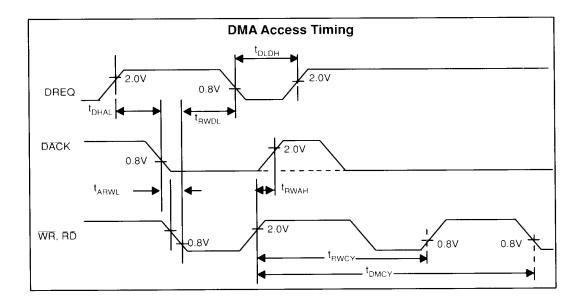

| DMA Access                                                        |                   |                 |                   |      |      |      |

|-------------------------------------------------------------------|-------------------|-----------------|-------------------|------|------|------|

|                                                                   |                   |                 | Values            |      |      |      |

| Parameter                                                         | Designator        | Test Conditions | Min.              | Тур. | Max. | Unit |

| DREQ High to DACK Low                                             | t <sub>DHAL</sub> |                 | 0                 |      |      | ns   |

| WR and RD Service Time<br>(From DACK Low to WR or RD<br>Low)      | t <sub>ARWL</sub> |                 | 40                |      |      | ns   |

| DREQ Release Time<br>(From WR or RD Low to DREQ Low) <sup>1</sup> | t <sub>RWDL</sub> | CL = 30 pF      | 35                |      | 150  | ns   |

| DACK Hold Time<br>(From WR or RD High to DACK Low)                | t <sub>RWAH</sub> |                 | 10                |      |      | ns   |

| DREG Interval<br>(From DREQ Low to DREQ High)                     | t <sub>DLDH</sub> |                 | 0                 |      |      | ns   |

| DREG Access Cycle Time (1)                                        | t <sub>RWCY</sub> |                 | 2t <sub>CLF</sub> |      |      | ns   |

| DREG Access Cycle Time (2)                                        | t <sub>DMCY</sub> |                 | 3t <sub>CLF</sub> |      |      | ns   |

Note: 1 The WR parameter is applicable when the data buffer register is full; the RD parameter is applicable when the data buffer register is empty.

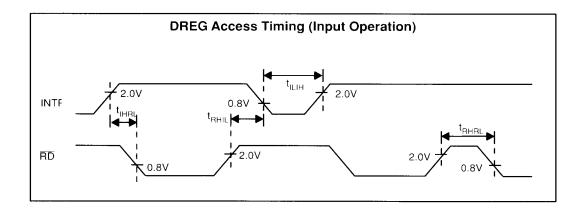

| DREG Access – Program Transfer with INTR (Input Operation) |                   |                 |        |      |      |      |  |

|------------------------------------------------------------|-------------------|-----------------|--------|------|------|------|--|

| B                                                          |                   |                 | Values |      |      |      |  |

| Parameter                                                  | Designator        | Test Conditions | Min.   | Тур. | Max. | Unit |  |

| RD Service Time<br>(From INTR High to RD Low)              | tIHRL             |                 | 0      |      |      | ns   |  |

| INTR Release Time<br>(From RD High to INTR Low)<br>(Note)  | t <sub>RHIL</sub> | CL = 20 pF      | 35     |      | 150  | ns   |  |

| INTR Recovery Time<br>(From INTR Low to INTR High)         | t <sub>sLIH</sub> |                 | 0      |      |      | ns   |  |

| RD Recovery Time<br>(From RD High to RD Low)               | t <sub>RHRL</sub> |                 | 50     |      |      | ns   |  |

**Note:** This parameter is applicable when the data buffer register is full in the output operation and empty in the input operation.

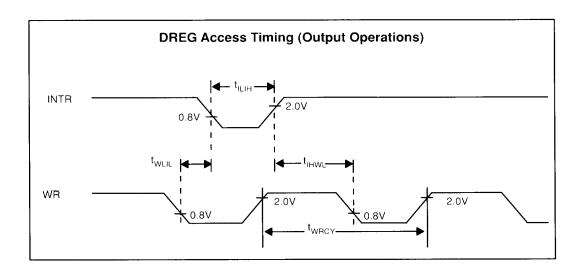

| DREG Access – Program Transfer with INTR (Output Operation) |                   |                 |                   |      |      |      |  |

|-------------------------------------------------------------|-------------------|-----------------|-------------------|------|------|------|--|

|                                                             |                   |                 |                   |      |      |      |  |

| Parameter                                                   | Designator        | Test Conditions | Min.              | Тур. | Max. | Unit |  |

| WR Service Time<br>(From INTR High to WR Low)               | t <sub>IHWL</sub> |                 | 0                 |      |      | ns   |  |

| INTR Release Time<br>(From WR High to INTR Low)<br>(Note)   | t <sub>WLIL</sub> | CL = 20 pF      | 35                |      | 150  | ns   |  |

| INTR Recovery Time<br>(From WR Low to INTR High)            | tiliH             |                 | 0                 |      |      | ns   |  |

| WR Cycle Time                                               | t <sub>WRCY</sub> |                 | 2t <sub>CLF</sub> |      |      | ns   |  |

**Note:** This parameter is applicable when the data buffer register is full in the output operation and empty in the input operation.

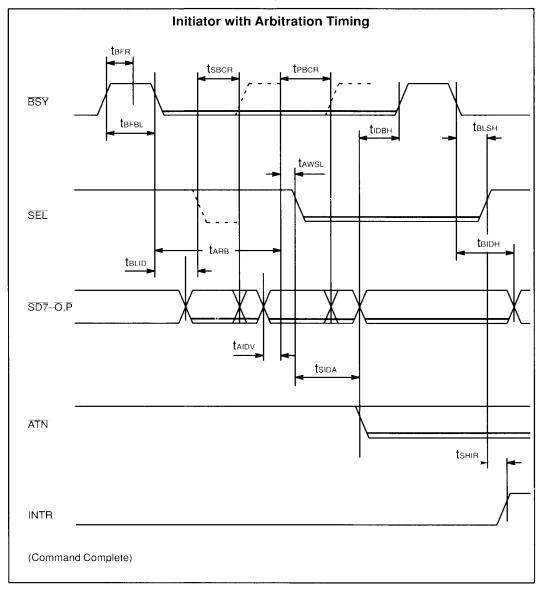

### **SCSI Bus Interface Selection Phase Timing**

| INITIATOR — Selection With                | Arbitration   |                       |        |                 |      |  |

|-------------------------------------------|---------------|-----------------------|--------|-----------------|------|--|

| _                                         |               |                       | Values |                 |      |  |

| Parameter                                 | Designator    | Min.                  | Тур.   | Max.            | Unit |  |

| Bus Free Time                             | <b>t</b> BFR  | 4 <b>t</b> clF+50     |        |                 | ns   |  |

| Start of Arbitration                      | <b>t</b> BFBL | (6+n)" x <b>t</b> clf |        | (7+n) x tclF+60 | ns   |  |

| BSY Low to Self ID# Output                | <b>t</b> BLID | 0                     |        | 60              | ns   |  |

| BSY Low to Prioritize                     | tarb          | 32 <b>t</b> clF60     |        |                 | ns   |  |

| Data Bus Valid to Prioritize              | taidv         | 200                   |        |                 | ns   |  |

| Bus Usage Permission Granted to SEL Low   | tawsl         | 0                     |        | 80              | ns   |  |

| SEL Low to Data Bus ID Output,<br>ATN Low | tsida         | 11 <b>t</b> cLF-30    |        |                 | ns   |  |

| Select ID# Output to BSY High             | tірвн         | 2 <b>t</b> clF-80     |        |                 | ns   |  |

| BSY Low to SEL High                       | <b>t</b> BLSH | 2tclf                 |        |                 | ns   |  |

| BSY Low to Select ID# Hold                | <b>t</b> BIDH | 2tclf                 |        |                 | ns   |  |

| SEL High to INTR High                     | <b>t</b> shir |                       |        | 60              | ns   |  |

| SEL Low to BSY High, ID Bit High          | tsbcr         |                       |        | 3tclF+180       | ns   |  |

| Prioritize to BSY High,<br>ID Bit High    | <b>t</b> PBCR |                       |        | 110             | ns   |  |

Notes: 'Bus Free Time: The minimum time period until the booked select command is executed. "TCL register value.

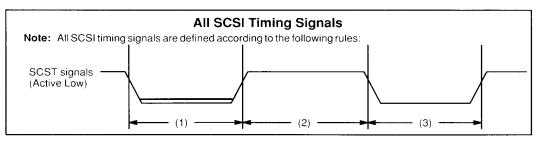

Notes:

- (1) The SPC outputs low level signal to the bus.

- (2) All devices hooked up to the bus do not output low level signals.

- (3) Other devices hooked up to the bus output low level signals.

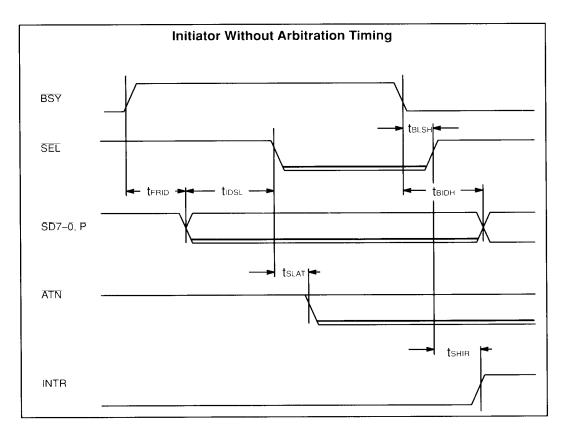

## **SCSI Bus Interface Selection Phase Timing**

| INITIATOR — Selection Wit     | hout Arbitrati | on                   |      |                  |      |

|-------------------------------|----------------|----------------------|------|------------------|------|

|                               |                |                      |      |                  |      |

| Parameter                     | Designator     | Min.                 | Тур. | Max.             | Unit |

| BSY High to Select ID# Output | <b>t</b> FRID  | (6+n) x <b>t</b> clf |      | (7+n) x tclF+140 | ns   |

| ID# Output to SEL Low         | <b>t</b> IDSL  | 11 <b>t</b> cLF-80   |      |                  | ns   |

| SEL Low to ATN Low            | <b>t</b> slat  | 11 <b>t</b> clF-80   |      |                  | ns   |

| BSY Low to SEL High           | <b>t</b> BLSH  | <b>2t</b> clf        |      |                  | ns   |

| BSY Low to ID# Hold           | tвірн          | <b>2</b> tclf        |      |                  | ns   |

| SEL High to INTR High         | <b>t</b> shir  |                      |      | 60               | ns   |

**Note:** n=TCL register set value.

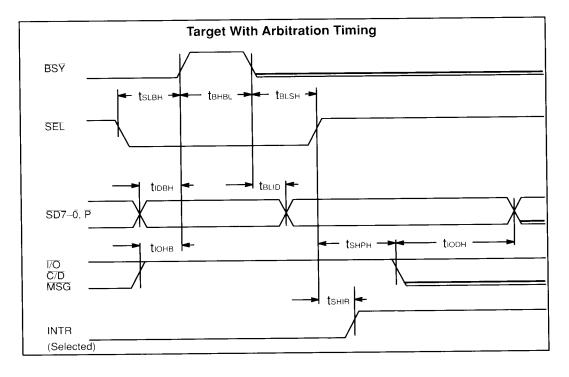

| TARGET — Selection With A        | rbitration    |                |        |                    |      |  |

|----------------------------------|---------------|----------------|--------|--------------------|------|--|

|                                  |               |                | Values |                    |      |  |

| Parameter                        | Designator    | Min.           | Тур.   | Max.               | Unit |  |

| SEL Low to BSY High              | tslвн         | 0              |        |                    | ns   |  |

| Data Bus Valid (ID#) to BSY High | tıрвн         | 0              |        |                    | ns   |  |

| I∕O High to BSY High             | tюнв          | 0              |        |                    | ns   |  |

| BSY High to BSY Low              | tвнвг         | 4tclf          |        | 5tclF+140          | ns   |  |

| BSY Low to ID# Hold              | <b>t</b> BLID | 60             |        |                    | ns   |  |

| BSY Low to SEL High              | <b>t</b> BLSH | 0              |        |                    | ns   |  |

| SEL High to Phase Signal Output  | <b>t</b> shph | 3tclF          |        | 4 <b>t</b> clF+160 | ns   |  |

| √O Low to Data Bus Output        | tione         | 7 <b>t</b> clf |        |                    | ns   |  |

| SEL High to INTR High            | <b>t</b> shir |                |        | 3tclF+130          | ns   |  |

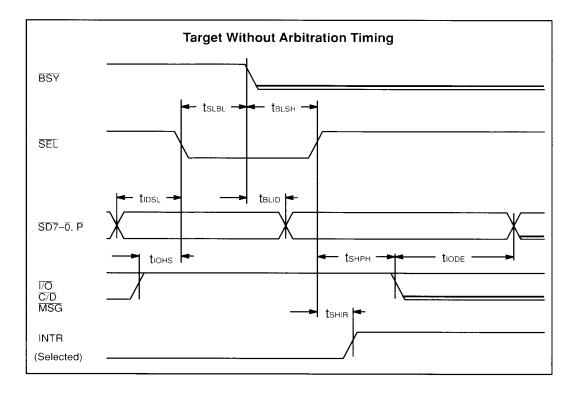

| TARGET — Selection Withou       | t Arbitration |                |      |                    |      |

|---------------------------------|---------------|----------------|------|--------------------|------|

| _                               |               |                |      |                    |      |

| Parameter                       | Designator    | Min.           | Тур. | Max.               | Unit |

| Data Bus Valid (ID#) to SEL Low | tidsl         | 0              |      |                    | ns   |

| √O High to SEL Low              | tıонs         | 0              |      |                    | ns   |

| SEL Low to BSY Low              | tslbl         | 2 <b>t</b> clf |      | 3tclF+130          | ns   |

| BSY Low to ID# Hold             | <b>t</b> BLID | 60             |      |                    | ns   |

| BSY Low to SEL High             | <b>t</b> BLSH | 0              |      |                    | ns   |

| SEL High to Phase Signal Output | tsнрн         | 3tolf          |      | 4 <b>t</b> clF+160 | ns   |

| I/O Low to Data Bus Output      | tiode         | 7 <b>t</b> clf |      |                    | ns   |

| SEL High to INTR High           | tshir         |                |      | 3tclF+130          | ns   |

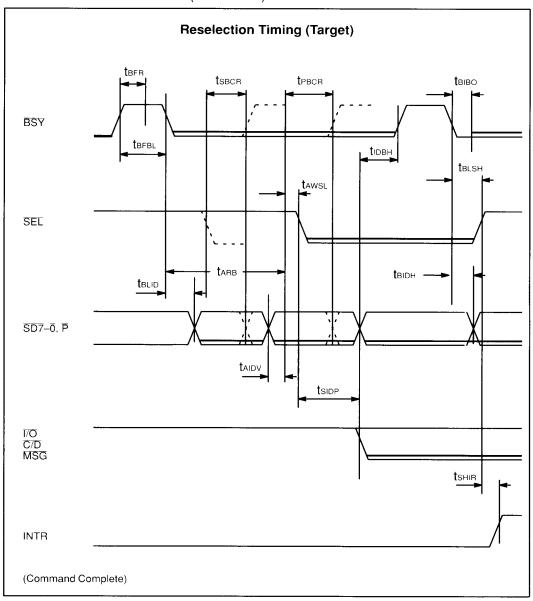

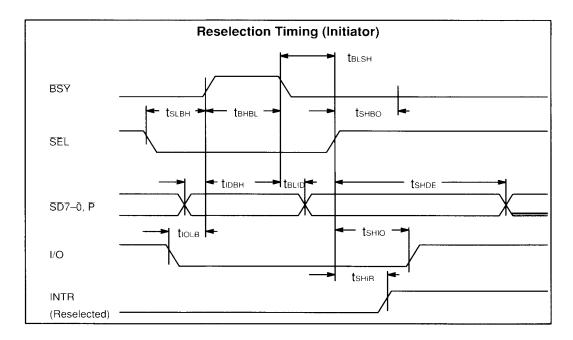

# SCSI BUS INTERFACE - RESELECTION PHASE TIMING

| Parameter                                             | Designator    | Values             |      |                          |      |

|-------------------------------------------------------|---------------|--------------------|------|--------------------------|------|

|                                                       |               | Min.               | Тур. | Max.                     | Unit |

| Bus Free Time                                         | <b>t</b> BFR  | 4 <b>t</b> CLF+50  |      |                          | ns   |

| Start of Arbitration                                  | <b>t</b> BFBL | (6+n)" x tclf      |      | (7+n) x <b>t</b> CLF+140 | ns   |

| BSY Low to Self ID# Output                            | <b>t</b> BLID | 0                  |      | 60                       | ns   |

| BSY Low to Prioritize                                 | <b>t</b> arb  | 32tclF-60          |      |                          | ns   |

| Data Bus Valid to Prioritize                          | <b>t</b> aidv | 200                |      |                          | ns   |

| Bus Usage Permission Granted to SEL Low tawsL         | tawsl         | 0                  |      | 80                       | ns   |

| SEL Low to Data Bus ID Output,<br>Phase Signal Output | tside         | 11 <b>t</b> cLF-50 |      |                          | ns   |

| Select ID# Output to BSY High                         | <b>t</b> idbh | 2tclf-80           |      |                          | ns   |

| BSY Low to BSY Low Output                             | <b>t</b> віво | 2 <b>t</b> clF+20  |      | 3 <b>t</b> CLF+140       | ns   |

| BSY Low to SEL High                                   | <b>t</b> BLSH | 2tclf              |      |                          | ns   |

| BSY Low to Select ID# Hold                            | <b>t</b> BIDH | 2tclf              |      |                          | ns   |

| SEL High to INTR High                                 | <b>t</b> shir |                    |      | 60                       | ns   |

| SEL Low to BSY High, ID Bit High                      | <b>t</b> sbcr |                    |      | 3tclF+180                | ns   |

| Prioritize to BSY High.<br>ID Bit High                | <b>t</b> PBCR |                    |      | 110                      | ns   |

Notes: Bus Free Time:=The minimum time period till the booked select command is executed.

<sup>&</sup>quot;n=TCL register value

| INITIATOR — Reselection Phase Timing             |               |                |      |                    |      |

|--------------------------------------------------|---------------|----------------|------|--------------------|------|

| Parameter                                        |               |                |      |                    |      |

|                                                  | Designator    | Min.           | Тур. | Max.               | Unit |

| SEL Low to BSY High                              | tslвн         | 0              |      |                    | ns   |

| Data Bus Valid (ID#) to BSY High                 | <b>t</b> idbh | 0              |      |                    | ns   |

| √O Low to BSY High                               | <b>t</b> iolb | 0              |      |                    | ns   |

| BSY High to BSY Low                              | <b>t</b> внвг | 4 <b>t</b> clf |      | 5tclF+140          | ns   |

| BSY Low to ID# Hold                              | <b>t</b> BLID | 60             |      |                    | ns   |

| BSY Low to SEL High                              | <b>t</b> BLSH | 0              |      |                    | ns   |

| SEL High to BSY Low Output                       | <b>t</b> shbo | 2 <b>t</b> clf |      | 3 <b>t</b> CLF+140 | ns   |

| SEL High to Data Bus Valid<br>(When I/O is High) | <b>t</b> shde | 3tclF+30       |      | 4tclF+160          | ns   |

| SEL High to 170 High                             | <b>t</b> shio | 200            |      |                    | ns   |

| SEL High to INTR High                            | <b>t</b> shir |                |      | 3tcLF+130          | ns   |

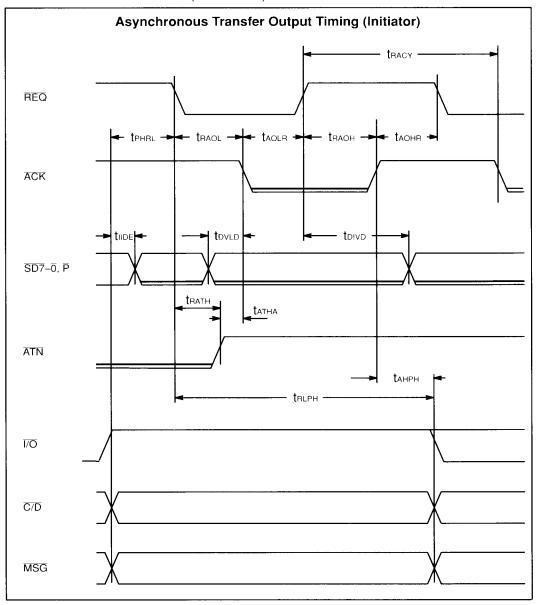

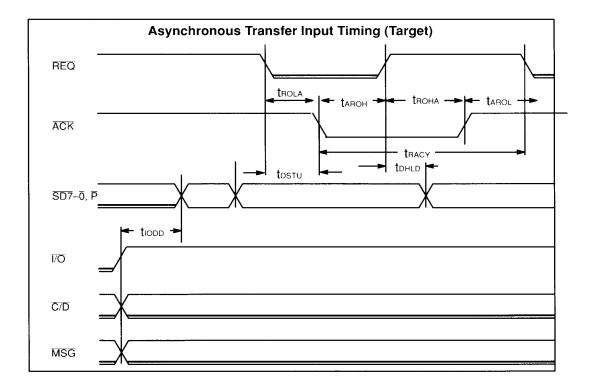

## SCSI BUS INTERFACE - INFORMATION TRANSFER PHASE TIMING

| Parameter                             |                       | Values         |      |      |      |

|---------------------------------------|-----------------------|----------------|------|------|------|

|                                       | Designator            | Min.           | Тур. | Max. | Unit |

| √O High to Data Bus Output            | tiide                 | 10             |      |      | ns   |

| Phase Set to REQ Low                  | tрняц                 | 100            |      |      | ns   |

| REQ Low to ACK Low                    | <b>t</b> raol         | 20             |      |      | ns   |

| Data Bus Valid to ACK Low             | <b>t</b> dvld         | 2tclF-80       |      |      | ns   |

| ACK Low to REQ High                   | <b>t</b> aolr         | 0              |      |      | ns   |

| REQ High to ACK High                  | trаон                 | 10             |      |      | ns   |

| ACK High to REQ Low                   | <b>t</b> aohr         | 0              |      |      | ns   |

| REQ High to ACK Low                   | <b>t</b> racy         | 2tclf          |      |      | ns   |

| REQ High to Data Bus Hold             | <b>d</b> via <b>t</b> | 15             |      |      | ns   |

| REQ Low to ATN High1                  | <b>t</b> rath         | 2tclf          |      |      | ns   |

| ATN High to ACK Low <sup>1</sup>      | <b>t</b> atha         | tclf-20        |      |      | ns   |

| REQ Low to Phase Change <sup>2</sup>  | tягрн                 | 3 <b>t</b> clf |      |      | ns   |

| ACK High to Phase Change <sup>2</sup> | tahph                 | 10             |      |      | ns   |

Notes: 1 This spec is applicable to the last byte transfer of message out phase in hardware transfer mode. 2 When the transfer phase is changed, both t<sub>RLPH</sub> and t<sub>ALPH</sub> should be specified.

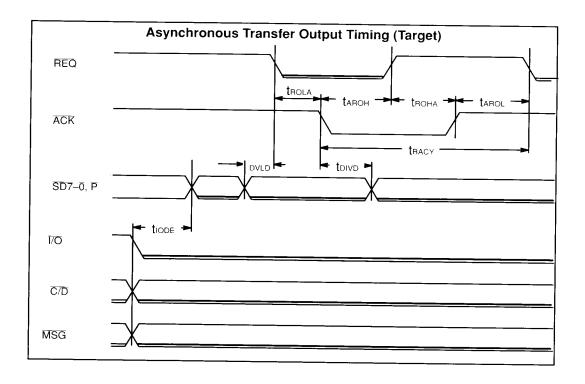

| TARGET —Asynchronous Transfer Output |               |                   |      |      |      |  |

|--------------------------------------|---------------|-------------------|------|------|------|--|

| Parameter                            |               | Values            |      |      |      |  |

|                                      | Designator    | Min.              | Тур. | Max. | Unit |  |

| √O Low to Data Bus Output            | tiode         | 7 <b>t</b> clf    |      |      | ns   |  |

| Data Bus Valid to REQ Low            | tovlo         | 2 <b>t</b> clF-80 |      |      | ns   |  |

| ACK Low to Data Bus Hold             | tolva         | 15                |      |      | ns   |  |

| REQ Low to ACK Low                   | <b>t</b> rola | 0                 |      |      | ns   |  |

| ACK Low to REQ High                  | <b>t</b> aroh | 10                |      | 180  | ns   |  |

| REQ High to ACK High                 | <b>t</b> roha | 0                 |      |      | ns   |  |

| ACK High to REQ Low                  | tarol         | 10                |      |      | ns   |  |

| ACK Low to REQ Low                   | tracy         | 2tclf             |      |      | ns   |  |

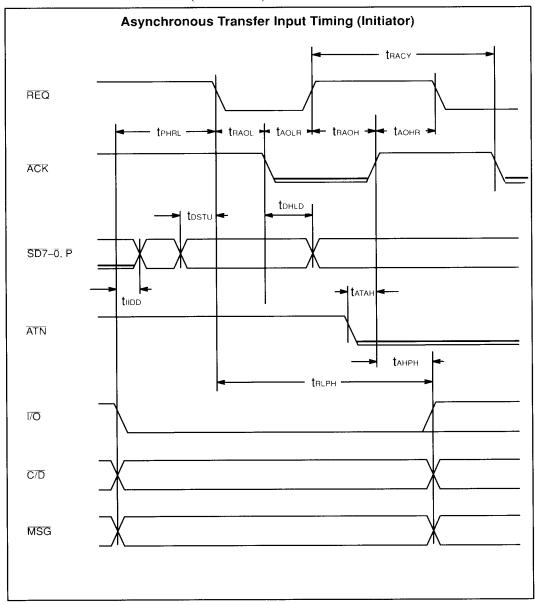

| INITIATOR —Asynchronous Transfer Input |               |         |      |                                        |      |  |

|----------------------------------------|---------------|---------|------|----------------------------------------|------|--|

| Parameter                              |               | Values  |      |                                        |      |  |

|                                        | Designator    | Min.    | Тур. | Max.                                   | Unit |  |

| √O Low to Data Bus Output Terminate    | <b>t</b> iidd |         |      | 140                                    | ns   |  |

| Phase Set to REQ Low                   | <b>t</b> PHRL | 100     |      |                                        | ns   |  |

| Data Bus Valid to REQ Low              | <b>t</b> ostu | 10      |      |                                        | ns   |  |

| REQ Low to ACK Low                     | <b>t</b> raol | 20      |      | **                                     | ns   |  |

| ACK Low to REQ High                    | <b>t</b> aolr | 0       |      |                                        | ns   |  |

| ACK Low to Data Bus Hold               | <b>t</b> DHLD | 15      |      | _                                      | ns   |  |

| REQ High to ACK High                   | <b>t</b> raoh | 10      |      |                                        | ns   |  |

| ACK High to REQ Low                    | taohr         | 0       |      | · · ·                                  | ns   |  |

| REQ High to ACK Low                    | tracy         | 2tclf   |      |                                        | ns   |  |

| ATN Low to ACK High <sup>1</sup>       | <b>t</b> atah | tclf-20 |      |                                        | ns   |  |

| REQ Low to Phase Change <sup>2</sup>   | tпLPH         | 3tolf   |      | ······································ | ns   |  |

| ACK High to Phase Change <sup>2</sup>  | tанрн         | 10      |      |                                        | ns   |  |

Notes: 1 Applicable to the last byte transfer of message out phase in hardware transfer mode.

<sup>2</sup> When the transfer phase is changed, both  $t_{\text{RLPH}}$  and  $t_{\text{AHPH}}$  should be specified.

| TARGET —Asynchronous Transfer Input   |               |       |        |      |      |

|---------------------------------------|---------------|-------|--------|------|------|

|                                       |               |       | Values |      |      |

| Parameter                             | Designator    | Min.  | Тур.   | Max. | Unit |

| I∕O High to Data Bus Output Terminate | tiodd         |       |        | 30   | ns   |

| Data Bus Valid to ACK Low             | <b>t</b> ostu | 10    |        |      | ns   |

| REQ High to Data Bus Hold             | <b>t</b> DHLD | 15    |        |      | ns   |

| REQ Low to ACK Low                    | <b>t</b> rola | 0     |        |      | ns   |

| ACK Low to REQ High                   | <b>t</b> aroh | 10    |        | 180  | ns   |

| REQ High to ACK High                  | <b>t</b> roha | 0     |        |      | ns   |

| ACK High to REQ Low                   | <b>t</b> arol | 10    |        |      | ns   |

| ACK Low to REQ Low                    | tracy         | 2tclf |        |      | ns   |

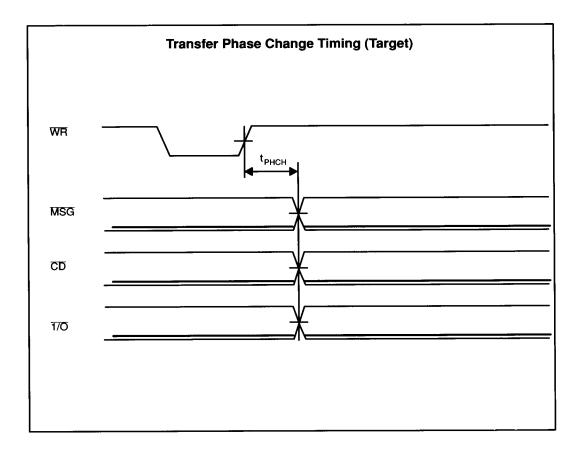

| Transfer Phase Change (Target)       |                   |      |        |      |      |

|--------------------------------------|-------------------|------|--------|------|------|

|                                      |                   |      | Values |      |      |

| Parameter                            | Designator        | Min. | Тур.   | Max. | Unit |

| From WR High to MSG, C/D, I/O change | t <sub>PHCH</sub> | 10   |        | 130  | ns   |

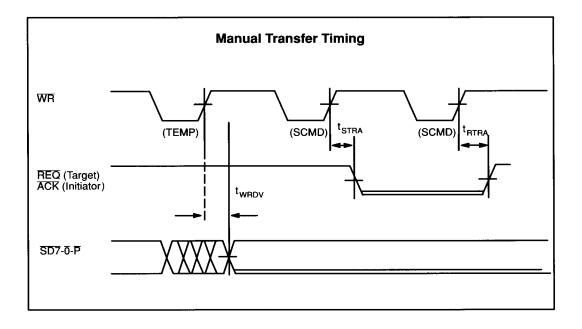

| Manual Transfer                                                    |                   |                   |        |                        |      |

|--------------------------------------------------------------------|-------------------|-------------------|--------|------------------------|------|

|                                                                    |                   |                   | Values | -                      |      |

| Parameter                                                          | Designator        | Min.              | Тур.   | Max.                   | Unit |

| From WR High to Data Bus Valid forTEMP Register                    | t <sub>WRDV</sub> |                   |        | 130                    | ns   |

| From WR High to REQ Low,<br>ACK Low for SET ACK/REQ<br>Command     | t <sub>STRA</sub> | 2t <sub>CLF</sub> |        | 3t <sub>CLF</sub> + 90 | ns   |

| From WR High to REQ High,<br>ACK High for RESET ACK/REQ<br>Command | t <sub>RTRA</sub> | 2t <sub>CLF</sub> |        | 3t <sub>CLF</sub> + 90 | ns   |

Note: Timing relationships not shown are the same as those for asynchronous transfers.

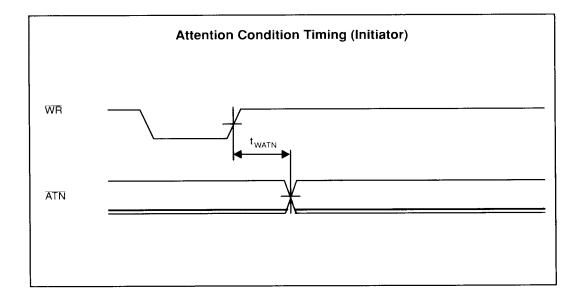

### SCSI BUS INTERFACE - ATTENTION CONDITION

| INITIATOR - Attention Condi                           | tion              |                   |      |                        |      |  |  |

|-------------------------------------------------------|-------------------|-------------------|------|------------------------|------|--|--|

|                                                       | Values            |                   |      |                        |      |  |  |

| Parameter                                             | Designator        | Min.              | Тур. | Max.                   | Unit |  |  |

| From WR High to ATN Change<br>(SET/RESET ATN Command) | t <sub>WATN</sub> | 2t <sub>CLF</sub> |      | 3t <sub>CLF</sub> + 90 | ns   |  |  |

Fast Track to SCSI MB89352

## **AC CHARACTERISTICS** (Continued)

### SCSI BUS INTERFACE - BUS FREE

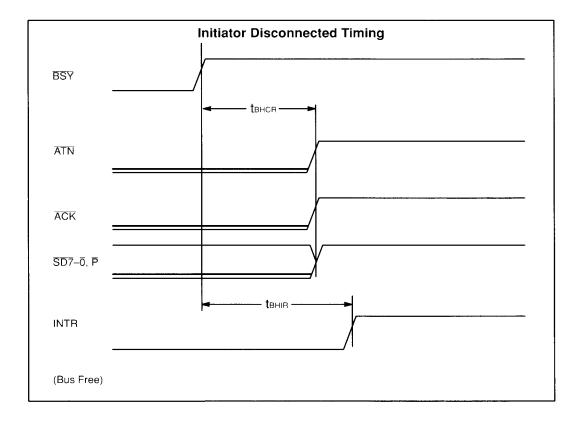

| INITIATOR — Bus Free (Disconnection) |                   |      |      |                   |      |  |

|--------------------------------------|-------------------|------|------|-------------------|------|--|

| _                                    |                   |      |      |                   |      |  |

| Parameter                            | Designator        | Min. | Тур. | Max.              | Unit |  |

| BSY High to Bus Clear                | t <sub>BHCR</sub> |      |      | 5tclF+140         | ns   |  |

| BSY High to INTR High                | t <sub>BHIR</sub> |      |      | 6 <b>t</b> CLF+80 | ns   |  |

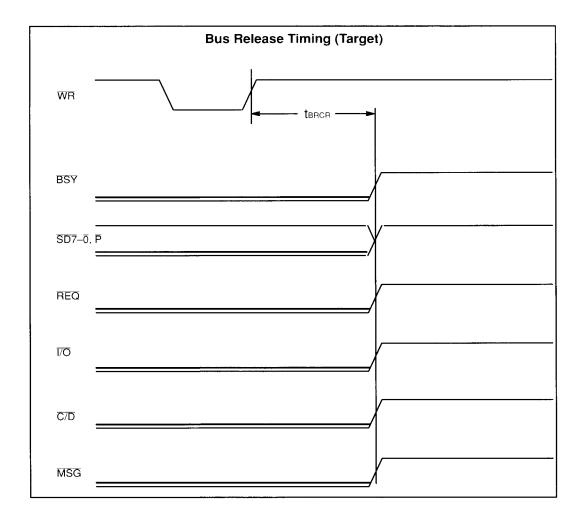

| TARGET (Bus Release Comm                      | and)              |      |        |           |      |

|-----------------------------------------------|-------------------|------|--------|-----------|------|

| _                                             |                   |      | Values |           |      |

| Parameter                                     | Designator        | Min. | Тур.   | Max.      | Unit |

| WR High to Bus Clear<br>(Bus Release Command) | t <sub>BRCR</sub> |      |        | 3tclF+100 | ns   |

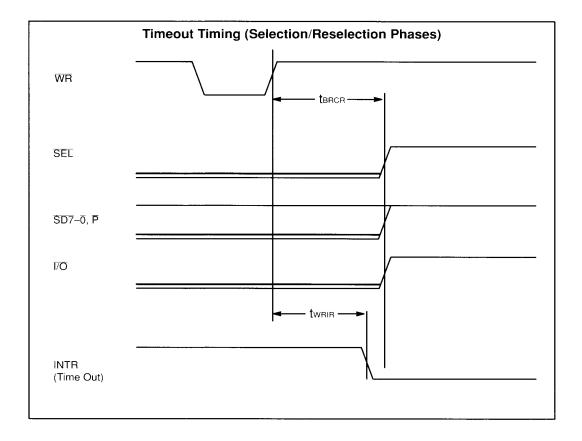

| TERMINATION (Time Out) – Selection and Reselection Phases        |                   |        |      |           |          |  |

|------------------------------------------------------------------|-------------------|--------|------|-----------|----------|--|

|                                                                  |                   | Values |      |           |          |  |

| Parameter                                                        | Designator        | Min.   | Тур. | Max.      | Unit     |  |

| WR High to SEL, SD7–0, P, I/O High (Reset Time Out Interruption) | t <sub>BRCR</sub> |        |      | 3tclF+100 | ns<br>ns |  |

| WR High to INTR Low                                              | t <sub>WRIR</sub> |        |      | 3tclF+60  | ns       |  |

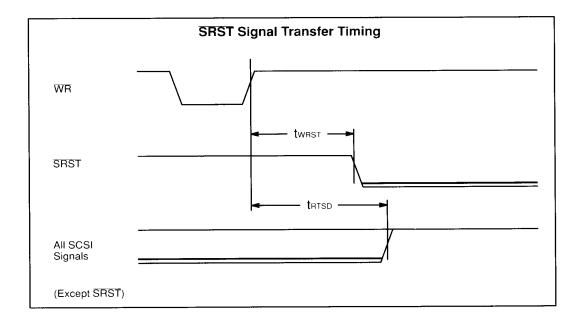

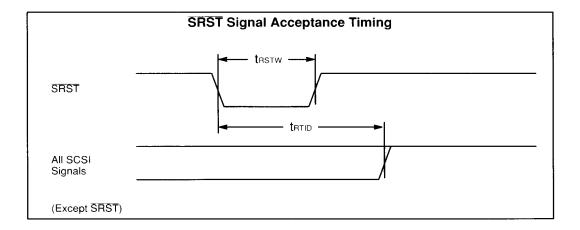

### SCSI BUS INTERFACE - RESET CONDITION

| SRST – Reset Condition (Output)                  |                   |        |      |      |      |  |

|--------------------------------------------------|-------------------|--------|------|------|------|--|

|                                                  |                   | Values |      |      |      |  |

| Parameter                                        | Designator        | Min.   | Тур. | Max. | Unit |  |

| WR High to SRST Low<br>(Write "I" to SCMD Bit-4) | twrst             | 10     |      | 110  | ns   |  |

| Reset Delay                                      | t <sub>RTSD</sub> |        |      | 140  | ns   |  |

### SCSI BUS INTERFACE - RESET CONDITION

| SRST – Reset Condition (Input) |                   |                   |      |                         |      |

|--------------------------------|-------------------|-------------------|------|-------------------------|------|

| _                              |                   | Values            |      |                         |      |

| Parameter                      | Designator        | Min.              | Тур. | Max.                    | Unit |

| SRST Pulse Width               | t <sub>RSTW</sub> | 3t <sub>CLF</sub> |      |                         | ns   |

| Reset Delay                    | t <sub>RTID</sub> |                   |      | 4t <sub>CLF</sub> + 200 | ns   |

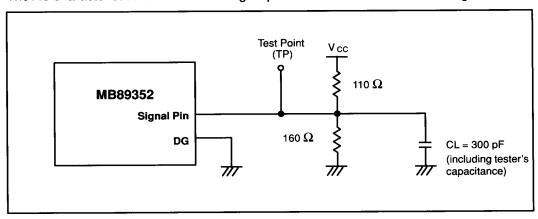

| Capacitance                                  |      |      |      |  |  |

|----------------------------------------------|------|------|------|--|--|

|                                              | V    |      |      |  |  |